延时开关用于仿真某一时刻闭合或断开的元件特性,这不是SPICE的基本元件,PSpice中使用了两个子电路模块来实现这一功能:初始时刻闭合,某一时刻断开的Sw_tOpen;初始时刻断开,某一时刻闭合的Sw_tClose。

这两个元件原理图符号位于eval.olb库中,SPICE实现位于anl_misc.lib库中,下面对其参数及实现做一总结。

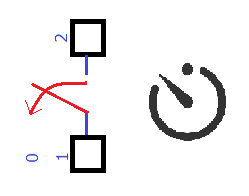

Sw_tOpen

SPICE实现:

1 | * For DC and AC analyses, the switch will be Closed. |

可以看到,Sw_tOpen是由一个压控开关和一个脉冲电压源组成的,tOpen前电阻为Rclosed,之后ttran时间内电阻以指数形式变化至Ropen,并保持10k秒。

| 参数 | 含义 | 默认值 |

|---|---|---|

| TOPEN | 断开切换时间 | 0 |

| TTRAN | 过渡时间 | 1u |

| RCLOSED | 导通电阻 | 0.01 |

| ROPEN | 开路电阻 | 1Meg |

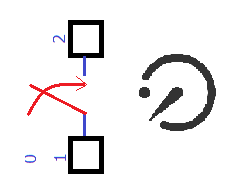

Sw_tClose

SPICE实现:

1 | * For DC and AC analyses, the switch will be Open. |

与Sw_tOpen基本完全相同,只是开始时是断开的,tClose后导通。

| 参数 | 含义 | 默认值 |

|---|---|---|

| TCLOSE | 导通切换时间 | 0 |

| TTRAN | 过渡时间 | 1u |

| RCLOSED | 导通电阻 | 0.01 |

| ROPEN | 开路电阻 | 1Meg |

需要注意的是,默认的RCLOSED和ROPEN的值不一定合适,需要根据实际电路进行修改,而且根据注释说明,这两个值之间的差距还不能太大,也就是说其实这两个元件是无法很好的模拟仿真理想开关的性质的。